#### A Model Based System-On-Chip Design Methodology: SystemC in practice

Yves Vanderperren, Wim Dehaene

yves.vanderperren@esat.kuleuven.ac.be

Katholieke Universiteit Leuven

Department of Electrical Engineering (ESAT)

#### Note

This presentation summarizes the work done at Alcatel Microelectronics in 2001, as published in:

"SystemC – Methodologies and Applications"

Kluwer Academic Publishers, July 2003

ISBN: 1402074794

EUROPEAN SYSTEM C"USERS GROUP

Presentations at 5th and 6th European SystemC Users Group Meetings

#### Outline

- Stating the case

- Evolution towards SoC

- Concrete example: the OFDM Wireless LAN Project at AmE

- Methodology overview

- Process

- Modelling Strategies

- Role of SystemC

- SystemC Modelling

- Model Refinement and Verification

- Conclusions

Presentation at Cetic - 12th Feb 2004 - Y. Vanderperren, W. Dehaene

## Stating the case: Evolution towards SoC

- Evolution of Manufacturing Technology

- smaller feature size

- with possibility of larger functions on the die

- Evolution of System Designs

- oxdot get ultimately single chip ( SoC ) for reasons of

- cost saving

- compactibility

- SoC are complex and contain many components: Hw,Fw,Sw

- all must inter-operate correctly and

- must fit to Customer specifications

- must be developed with faster-time-to-market

# Need for System-on-Chip (SoC) Design Methodology

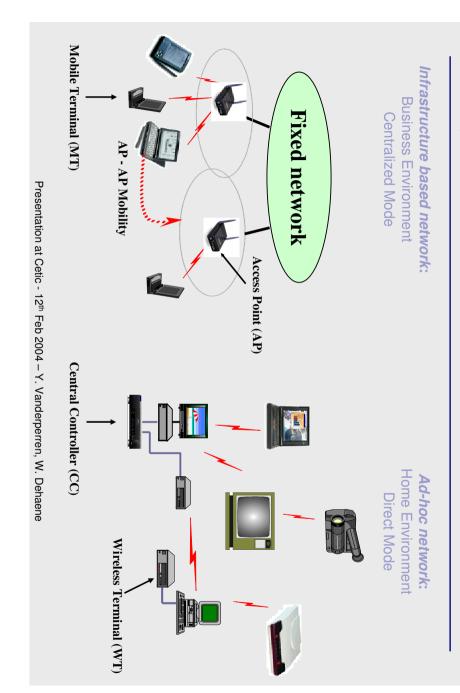

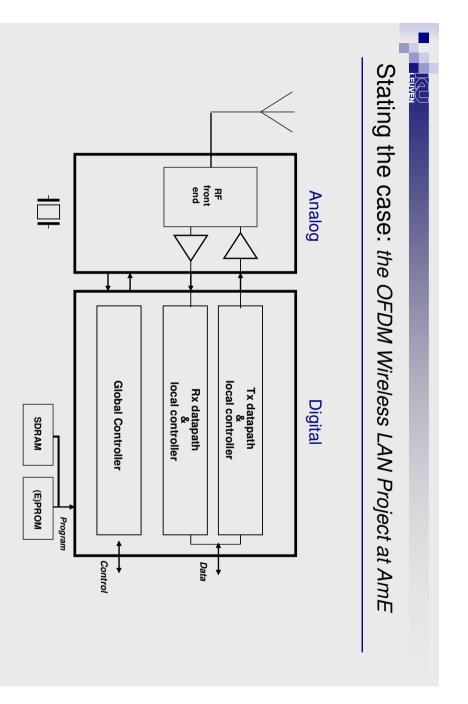

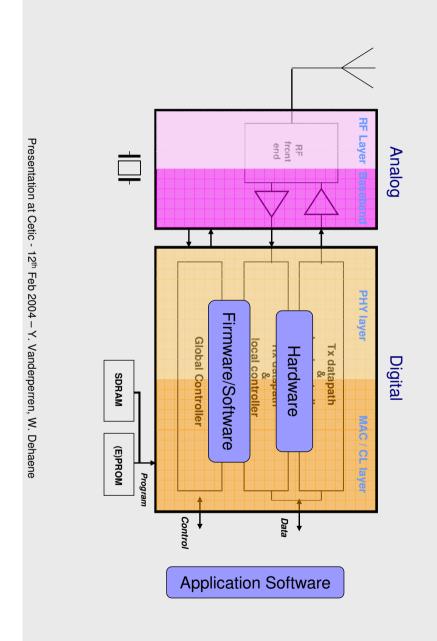

#### Stating the case: the OFDM Wireless LAN Project at AmE

#### Stating the case: the OFDM Wireless LAN Project at AmE

#### Outline

- Stating the case

- □ Evolution towards SoC

- Concrete example: the OFDM Wireless LAN Project at AmE

- Methodology overview

- Process

- Modelling Strategies

- Role of SystemC

- SystemC Modelling

- Model Refinement and Verification

- Conclusions

## Methodology Overview

- Iterative Development

- Refine system implementation to address risks early

- Use Case Driven Architecture

- Validate architectural design using Use Cases

- Visual Modelling: UML

- Executable System Models & Model-Centric Development

- Approach the design as a series of explorations and refinements

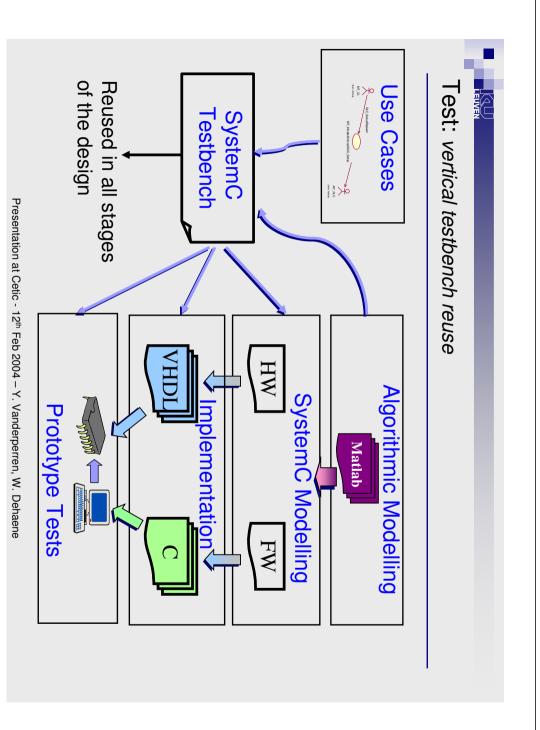

- lest

- Evolves during each iteration in parallel with system

- Allows efficient regression testing of each iteration

- Models reused throughout iterations

Presentation at Cetic - 12th Feb 2004 – Y. Vanderperren, W. Dehaene

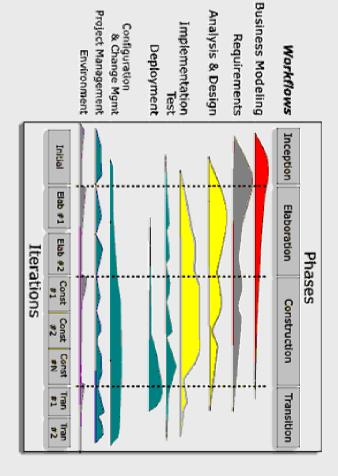

## Iterative Development

## Rational Unified Process (RUP)

## Iterative Development

|          |                                       | \<br>/                                     |                                       |                                      |                                 |

|----------|---------------------------------------|--------------------------------------------|---------------------------------------|--------------------------------------|---------------------------------|

|          | S<br>Feasibility,<br>Requirements and | It 0 A chitecture and High Level Modelling | It 1 Detailed Design and Cosimulation | It 2<br>Hardware Prototype<br>(FPGA) | It 3<br>Silicon                 |

| Customs  | Capture reats:                        | Spoits Architecture:                       | Cosimulation of                       | Cosimulation of SW                   | Cilion Varifica                 |

| dyalella | Capitale leque,                       | openity Architecture,                      | SystemC, VHDL and                     | on target and HW on                  | ollicon verilleanon,            |

|          | Agree Vision Doc;                     | Create HL SystemC /                        | SW                                    | FPGA;                                | Product                         |

|          | Create UC model;                      | UML model;                                 | :                                     | Conduct system                       | Qualification or                |

|          | Develop key algo's                    | Demonstrate<br>architecture meets          |                                       | V&V                                  | Topi Ovaio                      |

|          |                                       | project requirements                       |                                       |                                      |                                 |

| Hardware |                                       | Involvement with SystemC                   | Detailed Design of VHDL               | Port design to FPGA                  | Back end design and silicon fab |

|          |                                       | specification                              |                                       |                                      |                                 |

| Software |                                       | Specify SW Arch;                           | Build further SW                      | Build further                        | Build further SW                |

|          |                                       | Create Host-Based SW framework and         | framework;                            | It0/It1 framework                    | Tunctionality                   |

|          |                                       | basic functionality                        | Port to target                        |                                      |                                 |

| Model or | Matlab                                | SystemC: Matlab as                         | VHDL & C: SystemC                     | FPGA                                 | Product on silicon              |

| used     |                                       | oint operations                            | cosimulation                          |                                      |                                 |

| Test     | Function                              | Timing (TF mostly                          | Check design vs.                      | Full system                          | Full real-time                  |

| target   |                                       | CA for critical parts)                     | SystemC reference                     | operation                            | system operation                |

|          |                                       |                                            |                                       |                                      |                                 |

Presentation at Cetic - 12th Feb 2004 - Y. Vanderperren, W. Dehaene

### Use Case Analysis

- Mechanism to specify functional requirements related to toplevel view

- □ UC = a service providing value to an external entity

- UC's are basically textual a behavioural sequence

- UML diagrams help to organise and document

- For each UC we document a.o.:

- Primary (expected) system responses

- Secondary system responses

- (e.g. error conditions)

- Links to other UC's

scope of the system, user goals

### Use Case Analysis

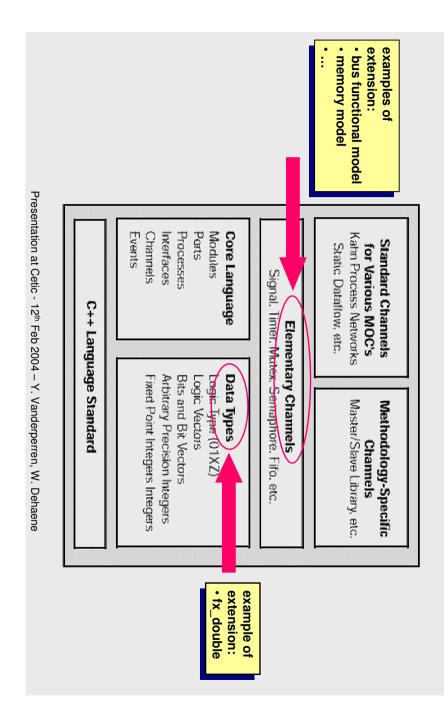

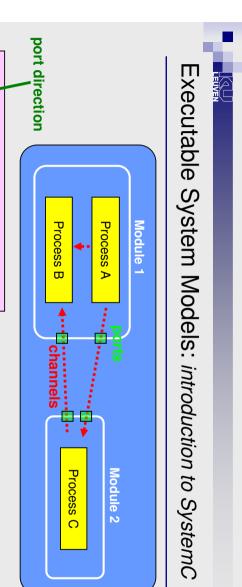

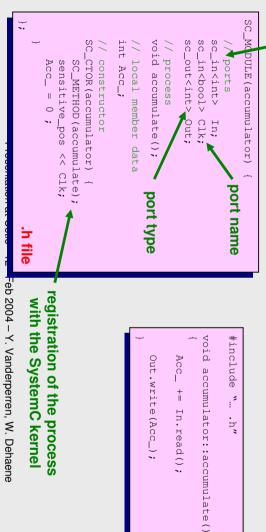

# Executable System Models: introduction to SystemC

- System design language for HW/SW co-design

- A library of C++ classes

- Processes

- Events

- Hardware data types

- Modules, ports

- Channels

✓ concurrency✓ time, reactivity✓ finite precision✓ hierarchy✓ communication

- A light-weight simulation kernel

- Allows to make an "Executable Specification"

#### Executable System Models: introduction to SystemC

.cc file

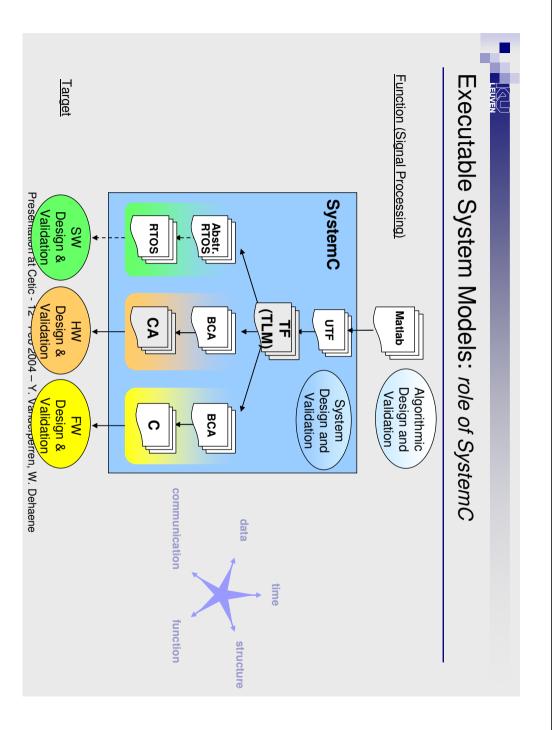

#### Executable System Models: role of SystemC

- An Executable Specification for communication with designers

- Designers participate in writing the specification knowledge transfer

- A Tool providing

- a starting point for HW implementation and verification

- detail the architecture for critical blocks

- do finite-precision design

- a platform serving as a HW model for SW development

- architecture, by running test scenarios an early verification of the overall system behavior and

- design space exploration

#### A Reference

testbenches are the starting point for all other testbenches and system test plans (Lab qualification)

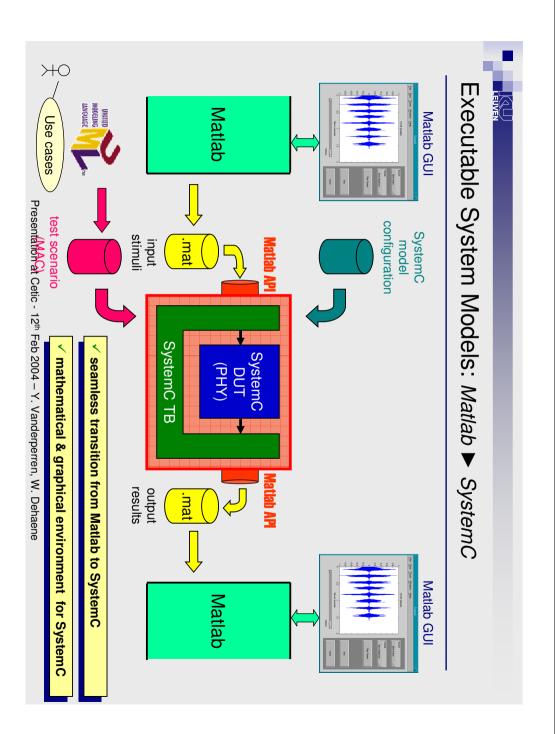

Conversion of the SystemC model to fixed-point

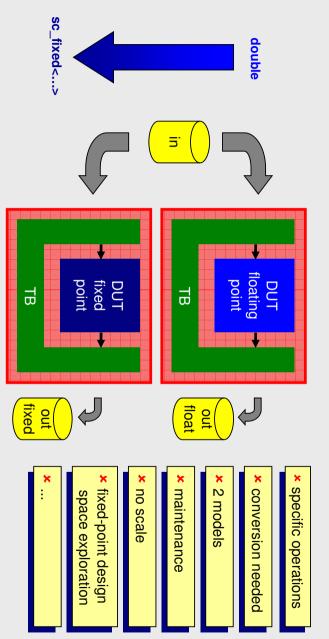

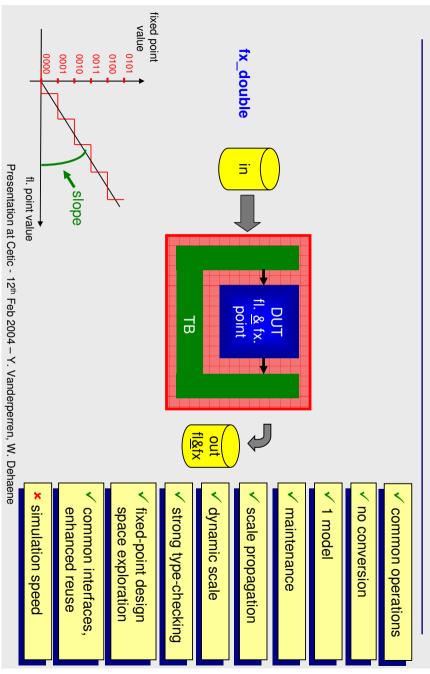

## Executable System Models: fixed-point design

Floating-Point SystemC

Fixed-Point design SystemC

space exploration **Fixed-Point**

- Conversion of the SystemC model to fixed-point

- Fixed-point design space exploration

- scale properly

- avoid overflow

- avoid quantization error

- minimize cost & power with precision constraint

- use as few bits as possible

#### Executable System Models: fixed-point design

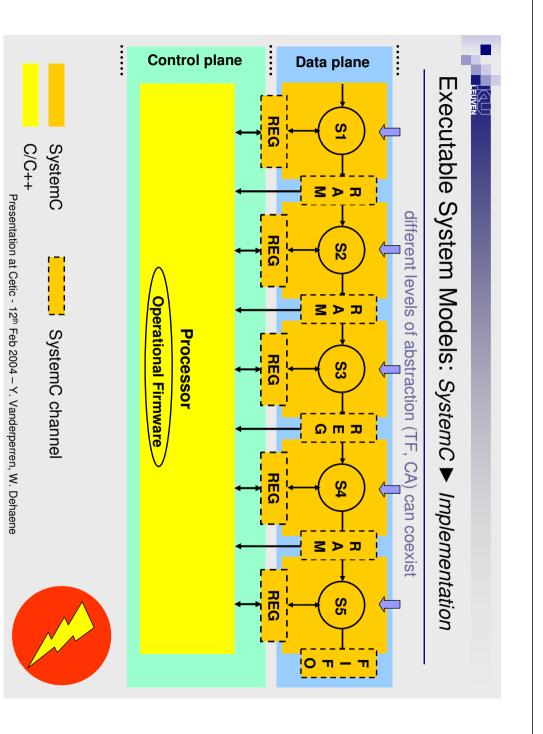

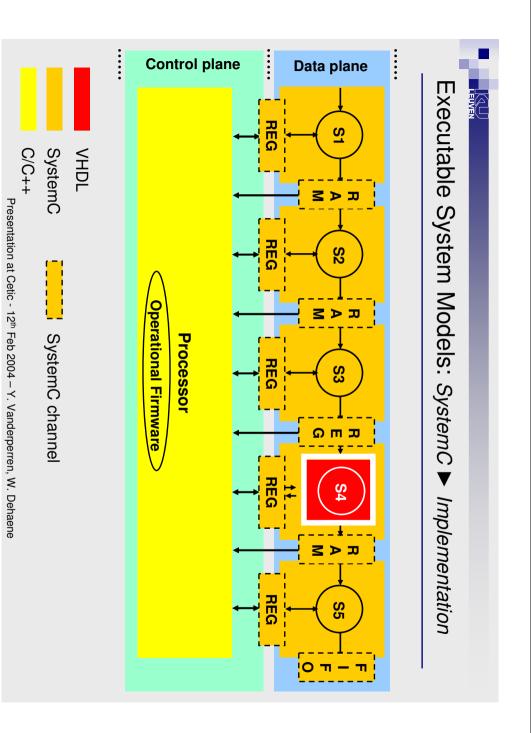

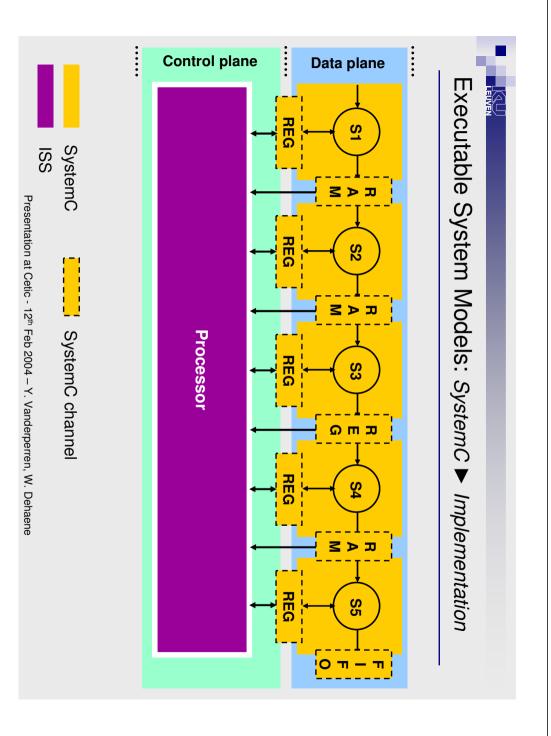

#### **Control plane** Data plane Executable S VHDL SSI SystemC ≥ ⊳ ਸ਼ System Models: REG S2 **≥** > ⊅ SystemC channel **Processor** SystemC ► S m Z REG *Implementation* REG S5 О П — П

#### Outline

- Stating the case

- Evolution towards SoC

- Concrete example: the OFDM Wireless LAN Project at AmE

- Methodology overview

- Process

- Modelling Strategies

- Role of SystemC

- SystemC Modelling

- Model Refinement and Verification

#### Conclusions

Presentation at Cetic - 12th Feb 2004 - Y. Vanderperren, W. Dehaene

#### Conclusions

- Besides the language, one needs also a Methodology

- Iterative based design: reducing risks, model based

- Iteration 0: SystemC model development

- executable specification as golden reference

- tool for early (designers/customers) feedback and design decisions

- Next iterations: design implementation, test and qualification

- SystemC model as reference & testbench reuse

- Experience from using SystemC and executable models: a.o.

- SystemC easy to learn and to use, extendable

- □ Executable spec. ⇒ no need for documentation

- SystemC 2x bridges the world of SW and HW

- same language base for both

- simulation speed

(abstract communication, TF level)

#### Conclusions

- Bottom line,

- Improved product quality

- meeting requirements

- early bug-detection

## Improved scheduling accuracy

much sounder basis for confident prediction of product release date than the traditional waterfall development

## Improved inter-disciplinary (system, hw, sw) cooperation

- cross-fertilisation of ideas

- better communications

## ☐ Improved confidence in the team

early and regular demonstrations of progress in tangible ways